## DAC80 DAC80P

# Monolithic 12-Bit DIGITAL-TO-ANALOG CONVERTERS

#### **FEATURES**

- INDUSTRY STANDARD PINOUT

- FULL ±10V SWING WITH V<sub>cc</sub> = ±12VDC

- DIGITAL INPUTS ARE TTL- AND CMOS-COMPATIBLE

- GUARANTEED SPECIFICATIONS WITH ±12V AND ±15V SUPPLIES

- ±1/2LSB MAXIMUM NONLINEARITY: 0°C to +70°C

- SETTLING TIME: 4μs max to ±0.01% of Full Scale

- GUARANTEED MONOTONICITY: 0°C to +70°C

- TWO PACKAGE OPTIONS: Hermetic sidebrazed ceramic and low-cost molded plastic

resistors, as well as low integral and differential linearity errors. Innovative circuit design enables the DAC80 to operate at supply voltages as low as ±11.4V with no loss in performance or accuracy over any range of output voltage. The lower power dissipation of this 118-mil by 121-mil chip results in higher reliability and greater long term stability.

Burr-Brown has further enhanced the reliability of the monolithic DAC80 by offering a hermetic, side-brazed, ceramic package. In addition, ease of use has been enhanced by eliminating the need for a +5V logic power supply.

For applications requiring both reliability and low cost, the DAC80P in a molded plastic package offers the same electrical performance over temperature as the ceramic model. The DAC80P is available with voltage output only.

For designs that require a wider temperature range, see Burr-Brown models DAC85H and DAC87H.

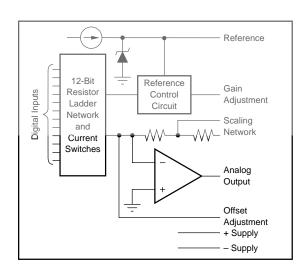

## **DESCRIPTION**

This monolithic digital-to-analog converter is pin-forpin equivalent to the industry standard DAC80 first introduced by Burr-Brown. Its single-chip design includes the output amplifier and provides a highly stable reference capable of supplying up to 2.5mA to an external load without degradation of D/A performance.

This converter uses proven circuit techniques to provide accurate and reliable performance over temperature and power supply variations. The use of a buried zener diode as the basis for the internal reference contributes to the high stability and low noise of the device. Advanced methods of laser trimming result in precision output current and output amplifier feedback

International Airport Industrial Park

• Mailing Address: PO Box 11400

• Tucson, AZ 85734

• Street Address: 6730 S. Tucson Blvd.

• Tucson, AZ 85706

Tel: (520) 746-1111

• Twx: 910-952-1111

• Cable: BBRCORP

• Telex: 066-6491

• FAX: (520) 889-1510

• Immediate Product Info: (800) 548-6132

## **SPECIFICATIONS**

#### **ELECTRICAL**

Typical at +25°C and  $\pm V_{CC}$  = 12V or 15V unless otherwise noted.

|                                                                             | DAC80       |                    |                |                          |  |

|-----------------------------------------------------------------------------|-------------|--------------------|----------------|--------------------------|--|

| PARAMETER                                                                   | MIN         | TYP                | MAX            | UNITS                    |  |

| DIGITAL INPUT                                                               |             |                    |                |                          |  |

| Resolution                                                                  |             |                    | 12             | Bits                     |  |

| Logic Levels (0°C to +70°C) <sup>(1)</sup> :<br>V <sub>IH</sub> (Logic "1") | +2          |                    | +16.5          | VDC                      |  |

| V <sub>II</sub> (Logic "0")                                                 | 0           |                    | +0.8           | VDC                      |  |

| $I_{IH}(V_{IN} = +2.4V)$                                                    |             |                    | +20            | μΑ                       |  |

| $I_{IL} (V_{IN} = +0.4V)$                                                   |             |                    | -180           | μΑ                       |  |

| ACCURACY (at +25°C)                                                         |             | 1474               | 14/0           | 1.00                     |  |

| Linearity Error<br>Differential Linearity Error                             |             | ±1/4<br>±1/2       | ±1/2<br>±3/4   | LSB<br>LSB               |  |

| Gain Error <sup>(2)</sup>                                                   |             | ±0.1               | ±0.3           | %                        |  |

| Offset Error <sup>(2)</sup>                                                 |             | ±0.05              | ±0.15          | % of FSR <sup>(3)</sup>  |  |

| DRIFT (0°C to +70°C)(4)                                                     |             |                    |                |                          |  |

| Total Bipolar Drift (includes gain, offset, and linearity drifts)           |             | ±10                | ±25            | ppm of FSR/°C            |  |

| Total Error Over 0°C to +70°C <sup>(5)</sup>                                |             |                    |                | 0, 1505                  |  |

| Unipolar<br>Bipolar                                                         |             | ±0.06<br>±0.06     | ±0.15<br>±0.12 | % of FSR<br>% of FSR     |  |

| Gain: Including Internal Reference                                          |             | ±10                | ±30            | ppm/°C                   |  |

| Excluding Internal Reference                                                |             | ±5                 | ±10            | ppm/°C                   |  |

| Unipolar Offset                                                             |             | ±1                 | ±3             | ppm of FSR/°C            |  |

| Bipolar Offset Differential Linearity 0°C to +70°C                          |             | ±7<br>±1/2         | ±15<br>±3/4    | ppm of FSR/°C<br>LSB     |  |

| Linearity Error 0°C to +70°C                                                |             | ±1/4               | ±1/2           | LSB                      |  |

| Monotonicity Guaranteed                                                     | 0           |                    | +70            | °C                       |  |

| CONVERSION SPEED, VOUT Models                                               |             |                    |                | 100                      |  |

| Settling Time to ±0.01% of FSR                                              |             |                    |                |                          |  |

| For FSR Change (2kΩ    500pF Load)                                          | 7/_         |                    |                |                          |  |

| with $10k\Omega$ Feedback with $5k\Omega$ Feedback                          |             | 3                  | 4              | μs                       |  |

| For 1LSB Change                                                             |             |                    | 4              | μs<br>μs                 |  |

| Slew Rate                                                                   | 10          | . III V            | AY             | V/μs                     |  |

| CONVERSION SPEED, I <sub>OUT</sub> Models Settling Time to ±0.01% of FSR    | Grou        | 300                | Lte            |                          |  |

| For FSR change: $10\Omega$ to $100\Omega$ Load $1k\Omega$ Load              |             | 1                  |                | ns<br>μs                 |  |

| ANALOG OUTPUT, V <sub>OUT</sub> Models                                      |             |                    |                |                          |  |

| Ranges                                                                      |             | 5, ±5, ±10, +5,    | +10            | V                        |  |

| Output Current <sup>(6)</sup>                                               | ±5          |                    |                | mA                       |  |

| Output Impedance (DC) Short Circuit to Common, Duration <sup>(7)</sup>      |             | 0.05<br>Indefinite |                | Ω                        |  |

|                                                                             |             | machinic           |                |                          |  |

| ANALOG OUTPUT, I <sub>OUT</sub> Models<br>Ranges: Bipolar                   | ±0.96       | ±1.0               | ±1.04          | mA                       |  |

| Unipolar                                                                    | -1.96       | -2.0               | -2.04          | mA                       |  |

| Output Impendance: Bipolar                                                  | 2.6         | 3.2                | 3.7            | kΩ                       |  |

| Unipolar<br>Compliance                                                      | 4.6<br>-2.5 | 6.6                | 8.6<br>+2.5    | kΩ<br>V                  |  |

| •                                                                           |             | . 0. 00            |                | V                        |  |

| REFERENCE VOLTAGE OUTPUT External Current (constant load)                   | +6.23       | +6.30              | +6.37<br>2.5   | w <sub>mA</sub>          |  |

| Drift vs Temperature                                                        |             | ±10                | ±20            | ppm/°C                   |  |

| Output Impedance                                                            |             | 1                  |                | Ω                        |  |

| POWER SUPPLY SENSITIVITY                                                    |             |                    |                |                          |  |

| $V_{CC} = \pm 12VDC$ or $\pm 15VDC$                                         |             | ±0.002             | ±0.006         | % FSR/ % V <sub>CC</sub> |  |

| POWER SUPPLY REQUIREMENTS                                                   |             |                    |                |                          |  |

| ±V <sub>CC</sub>                                                            | ±11.4       |                    | ±16.5          | VDC                      |  |

| Supply Drain (no load): +V <sub>CC</sub> -V <sub>CC</sub>                   |             | 8<br>15            | 12<br>20       | mA<br>mA                 |  |

| Power Dissipation ( $V_{CC} = \pm 15VDC$ )                                  |             | 345                | 480            | mW                       |  |

| TEMPERATURE RANGE                                                           |             |                    |                |                          |  |

| Specification                                                               | 0           |                    | +70            | °C                       |  |

| Operating                                                                   | -25         |                    | +85            | °C                       |  |

|                                                                             |             |                    |                |                          |  |

| Storage: Plastic DIP Ceramic DIP                                            | –60<br>–65  |                    | +100<br>+150   | °C<br>°C                 |  |

NOTES: (1) Refer to "Logic Input Compatibility" section. (2) Adjustable to zero with external trim potentiometer. (3) FSR means full scale range and is 20V for  $\pm$ 10V range, 10V for  $\pm$ 5V range for V<sub>OUT</sub> models; 2mA for I<sub>OUT</sub> models. (4) To maintain drift spec, internal feedback resistors must be used. (5) Includes the effects of gain, offset and linearity drift. Gain and offset errors externally adjusted to zero at +25°C. (6) For  $\pm$ V<sub>CC</sub> less than  $\pm$ 12VDC, limit output current load to  $\pm$ 2.5mA to maintain  $\pm$ 10V full scale output voltage swing. For output range of  $\pm$ 5V or less, the output current is  $\pm$ 5mA over entire  $\pm$ V<sub>CC</sub> range. (7) Short circuit current is 40mA, max.

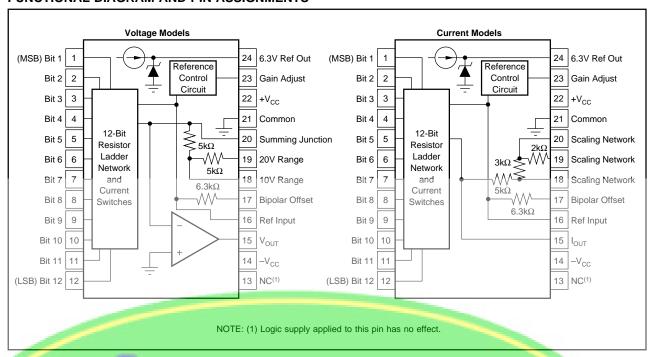

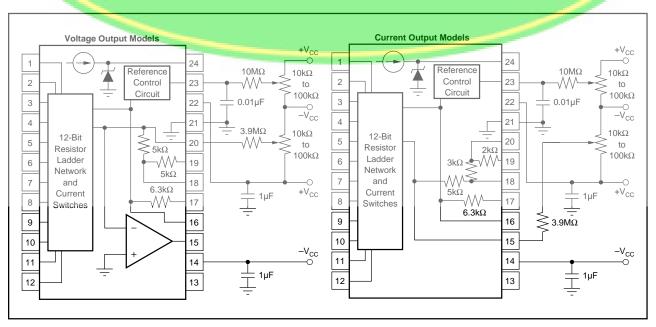

#### **FUNCTIONAL DIAGRAM AND PIN ASSIGNMENTS**

#### **ABSOLUTE MAXIMUM RATINGS**

| +V <sub>cc</sub> to Common                      | 0V to +18V       |

|-------------------------------------------------|------------------|

|                                                 | 0V to -18        |

| Digital Data Inputs to Common                   | -1V to +18V      |

| Reference Output to Common                      | ±V <sub>cc</sub> |

| Reference Input to Common                       | ±V <sub>cc</sub> |

| Bipolar Offset to Common                        | ±V <sub>cc</sub> |

| 10V Range R to Common                           | ±V <sub>cc</sub> |

| 20V Range R to Common                           | ±V <sub>cc</sub> |

| External Voltage to DAC Output                  | -5V to +5V       |

| Lead Temperature (soldering, 10s)               | +300°C           |

| Max Junction Temperature                        |                  |

| Thermal Resistance, $\theta_{JA}$ : Plastic DIP |                  |

| Ceramic DIP                                     | 65°C/W           |

|                                                 |                  |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### **ORDERING INFORMATION**

| ORDERING INI ORMATION    |                                                                                                   |  |  |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PACKAGE                  | OUTPUT                                                                                            |  |  |  |  |  |

| Ceramic DIP              | Current                                                                                           |  |  |  |  |  |

| Ceramic DIP              | Current                                                                                           |  |  |  |  |  |

| Ceramic DIP              | Voltage                                                                                           |  |  |  |  |  |

| Ceramic DIP              | Voltage                                                                                           |  |  |  |  |  |

| Plastic DIP              | Voltage                                                                                           |  |  |  |  |  |

| BURN-IN SCREENING OPTION |                                                                                                   |  |  |  |  |  |

|                          | BURN-IN TEMP.                                                                                     |  |  |  |  |  |

| DDEL PACKAGE             |                                                                                                   |  |  |  |  |  |

| Ceramic DIP              | +125°C                                                                                            |  |  |  |  |  |

| Plastic DIP              | +125°C                                                                                            |  |  |  |  |  |

|                          | PACKAGE  Ceramic DIP Ceramic DIP Ceramic DIP Ceramic DIP Plastic DIP  OPTION  PACKAGE Ceramic DIP |  |  |  |  |  |

NOTE: (1) Or equivalent combination. See text.

#### **PACKAGE INFORMATION**

|   | MODEL  | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|---|--------|--------------------|------------------------------------------|

| - | DAC80P | 24-Pin Plastic DIP | 167                                      |

|   | DAC80  | 24-Pin Ceramic DIP | 125                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

#### **BURN-IN SCREENING**

Burn-in screening is an option available for the models indicated in the Ordering Information table. Burn-in duration is 160 hours at the maximum specified grade operating temperature (or equivalent combination of time and temperature).

All units are tested after burn-in to ensure that grade specifications are met. To order burn-in, add "-BI" to the base model number.

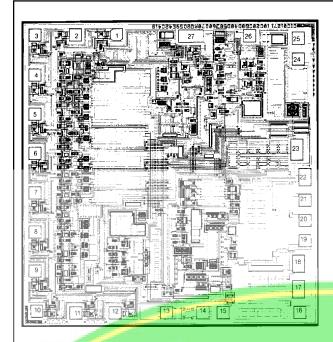

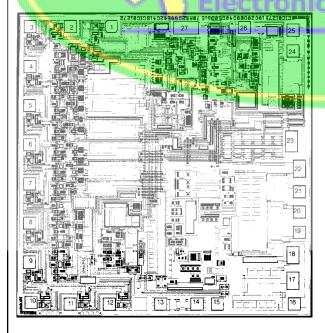

#### **DICE INFORMATION**

| PAD | FUNCTION     | PAD | FUNCTION         |

|-----|--------------|-----|------------------|

| 1   | Bit 1 (MSB)  | 15  | -V <sub>cc</sub> |

| 2   | Bit 2        | 16  | V <sub>OUT</sub> |

| 3   | Bit 3        | 17  | Ref In           |

| 4   | Bit 4        | 18  | Bipolar Offset   |

| 5   | Bit 5        | 19  | Scale 10V FSR    |

| 6   | Bit 6        | 20  | Scale 20V FSR    |

| 7   | Bit 7        | 21  | NC               |

| 8   | Bit 8        | 22  | Sum Junct        |

| 9   | Bit 9        | 23  | COM              |

| 10  | Bit 10       | 24  | COM              |

| 11  | Bit 11       | 25  | +V <sub>cc</sub> |

| 12  | Bit 12 (LSB) | 26  | Gain Adjust      |

| 13  | NC           | 27  | 6.3V Ref Out     |

| 14  | NC           |     |                  |

Substrate Bias: Isolated. NC: No Connection

#### **MECHANICAL INFORMATION**

|               | MILS (0.001") | MILLIMETERS       |

|---------------|---------------|-------------------|

| Die Size      | 118 x 121 ± 5 | 3.0 x 3.07 ± 0.13 |

| Die Thickness | 20 ± 3        | 0.51 ± 0.08       |

| Min. Pad Size | 4 x 4         | 0.10 x 0.10       |

| Metalization  |               | Aluminum          |

**DAC80KD-V DIE TOPOGRAPHY**

# CHAKCHAI

**DAC80KD-I DIE TOPOGRAPHY**

| PAD | FUNCTION     | PAD | FUNCTION         |

|-----|--------------|-----|------------------|

| 1   | Bit 1 (MSB)  | 15  | -V <sub>cc</sub> |

| 2   | Bit 2        | 16  | l <sub>out</sub> |

| 3   | Bit 3        | 17  | Ref In           |

| 4   | Bit 4        | 18  | Bipolar Offset   |

| 5   | Bit 5        | 19  | Scale 10V FSR    |

| 6   | Bit 6        | 20  | Scale 20V FSR    |

| 7   | Bit 7        | 21  | Scale            |

| 8   | Bit 8        | 22  | NC               |

| 9   | Bit 9        | 23  | COM              |

| 10  | Bit 10       | 24  | COM              |

| 11  | Bit 11       | 25  | +V <sub>CC</sub> |

| 12  | Bit 12 (LSB) | 26  | Gain Adjust      |

| 13  | NC           | 27  | 6.3V Ref Out     |

| 14  | NC           |     |                  |

Substrate Bias: Isolated. NC: No Connection

#### **MECHANICAL INFORMATION**

|               | MILS (0.001") | MILLIMETERS       |

|---------------|---------------|-------------------|

| Die Size      | 118 x 121 ± 5 | 3.0 x 3.07 ± 0.13 |

| Die Thickness | 20 ± 3        | $0.51 \pm 0.08$   |

| Min. Pad Size | 4 x 4         | 0.10 x 0.10       |

| Metalization  |               | Aluminum          |

# DISCUSSION OF SPECIFICATIONS

#### **DIGITAL INPUT CODES**

The DAC80 accepts complementary binary digital input codes. The CBI model may be connected by the user for any one of three complementary codes: CSB, COB, or CTC (see Table I).

| DIGITAL INPUT                                | ANALOG OUTPUT                                                  |                                             |                                                   |  |  |

|----------------------------------------------|----------------------------------------------------------------|---------------------------------------------|---------------------------------------------------|--|--|

| MSB LSB                                      | CSB<br>Complementary<br>Straight<br>Binary                     | COB<br>Complementary<br>Offset<br>Binary    | CTC <sup>(1)</sup> Complementary Two's Complement |  |  |

| 000000000000<br>011111111111<br>100000000000 | +Full Scale<br>+1/2 Full Scale<br>1/2 Full Scale –1LSB<br>Zero | +Full Scale<br>Zero<br>-1LSB<br>-Full Scale | -1LSB<br>-Full Scale<br>-Full Scale<br>Zero       |  |  |

NOTE: (1) Invert the MSB of the COB code with an external inverter to obtain CTC code.

TABLE I. Digital Input Codes.

#### **ACCURACY**

Linearity of a D/A converter is the true measure of its performance. The linearity error of the DAC80 is specified over its entire temperature range. This means that the analog output will not vary by more than  $\pm 1/2$ LSB, maximum, from an ideal straight line drawn between the end points (inputs all "1"s and all "0"s) over the specified temperature range of 0°C to +70°C.

Differential linearity error of a D/A converter is the deviation from an ideal 1LSB voltage change from one adjacent output state to the next. A differential linearity error specification of  $\pm 1/2$ LSB means that the output voltage step sizes can range from 1/2LSB to 3/2LSB when the input changes from one adjacent input state to the next.

Monotonicity over a  $0^{\circ}$ C to  $+70^{\circ}$ C range is guaranteed in the DAC80 to insure that the analog output will increase or remain the same for increasing input digital codes.

#### DRIFT

Gain Drift is a measure of the change in the full scale range output over temperature expressed in parts per million per °C (ppm/°C). Gain drift is established by: 1) testing the end point differences for each DAC80 model at 0°C, +25°C, and +70°C; 2) calculating the gain error with respect to the 25°C value, and; 3) dividing by the temperature change. This figure is expressed in ppm/°C and is given in the electrical specifications both with and without internal reference.

Offset Drift is a measure of the actual change in output with all "1"s on the input over the specified temperature range. The offset is measured at 0°C, +25°C, and 70°C. The maximum change in Offset is referenced to the Offset at 25°C and is divided by the temperature range. This drift is expressed in parts per million of full scale range per °C (ppm of FSR/°C).

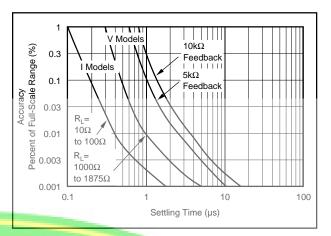

#### SETTLING TIME

Settling time for each DAC80 model is the total time (including slew time) required for the output to settle within an error band around its final value after a change in input (see Figure 1).

FIGURE 1. Full Scale Range Settling Time vs Accuracy.

#### **Voltage Output Models**

Three settling times are specified to ±0.01% of full scale range (FSR); two for maximum full scale range changes of 20V, 10V and one for a 1LSB change. The 1LSB change is measured at the major carry (0111...11 to 1000...00), the point at which the worst case settling time occurs.

#### **Current Output Models**

Two settling times are specified to  $\pm 0.01\%$  of FSR. Each is given for current models connected with two different resistive loads:  $10\Omega$  to  $100\Omega$  and  $1000\Omega$  to  $1875\Omega$ . Internal resistors are provided for connecting nominal load resistances of approximately  $1000\Omega$  to  $1800\Omega$  for output voltage range of  $\pm 1V$  and 0 to -2V (see Figures 11 and 12).

#### COMPLIANCE

Compliance voltage is the maximum voltage swing allowed on the current output node in order to maintain specified accuracy. The maximum compliance voltage of all current output models is  $\pm 2.5$ V. Maximum safe voltage range of  $\pm 1$ V and 0 to -2V (see Figures 11 and 12).

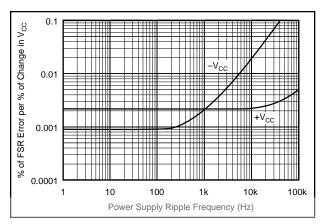

#### POWER SUPPLY SENSITIVITY

Power supply sensitivity is a measure of the effect of a power supply change on the D/A converter output. It is defined as a percent of FSR per percent of change in either the positive or negative supplies about the nominal power supply voltages (see Figure 2).

#### REFERENCE SUPPLY

All DAC80 models are supplied with an internal 6.3V reference voltage supply. This voltage (pin 24) has a tolerance of  $\pm 1\%$  and must be connected to the Reference Input

FIGURE 2. Power Supply Rejection vs Power Supply Ripple.

(pin 16) for specified operation. This reference may be used externally also, but external current drain is limited to 2.5mA.

If a varying load is to be driven, an external buffer amplifier is recommended to drive the load in order to isolate bipolar offset from load variations. Gain and bipolar offset adjustments should be made under constant load conditions.

#### LOGIC INPUT COMPATIBILITY

DAC80 digital inputs are TTL, LSTTL and 4000B, 54/74HC CMOS compatible. The input switching threshold remains at the TTL threshold over the entire supply range. Logic "0" input current over temperature is low enough to permit driving DAC80 directly from outputs of 4000B and 54/74C CMOS devices.

### **OPERATING INSTRUCTIONS**

#### **POWER SUPPLY CONNECTIONS**

Connect power supply voltages as shown in Figure 3. For optimum performance and noise rejection, power supply decoupling capacitors should be added as shown. These capacitors (1 $\mu$ F tantalum) should be located close to the DAC80.

#### ±12V OPERATION

All DAC80 models can operate over the entire power supply range of  $\pm 11.4$ V to  $\pm 16.5$ V. Even with supply levels dropping to  $\pm 11.4$ V, the DAC80 can swing a full  $\pm 10$ V range, provided the load current is limited to  $\pm 2.5$ mA. With power supplies greater than  $\pm 12$ V, the DAC80 output can be loaded up to  $\pm 5$ mA. For output swing of  $\pm 5$ V or less, the output current is  $\pm 5$ mA, minimum, over the entire  $V_{CC}$  range.

No bleed resistor is needed from  $+V_{CC}$  to pin 24, as was needed with prior hybrid Z versions of DAC80. Existing  $\pm 12V$  applications that are being converted to the monolithic DAC80 must omit the resistor to pin 24 to insure proper operation.

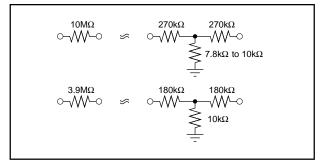

#### **EXTERNAL OFFSET AND GAIN ADJUSTMENT**

Offset and gain may be trimmed by installing external Offset and Gain potentiometers. Connect these potentiometers as shown in Figure 3 and adjust as described below. TCR of the potentiometers should be  $100\text{ppm/}^{\circ}\text{C}$  or less. The  $3.9\text{M}\Omega$  and  $10\text{M}\Omega$  resistors (20% carbon or better) should be located close to the DAC80 to prevent noise pickup. If it is not convenient to use these high value resistors, an equivalent "T" network, as shown in Figure 4, may be substituted.

FIGURE 3. Power Supply and External Adjustment Connection Diagrams.

FIGURE 4. Equivalent Resistances.

Existing applications that are converting to the monolithic DAC80 must change the gain trim resistor on pin 23 from  $33M\Omega$  to  $10M\Omega$  to insure sufficient adjustment range. Pin 23 is a high impedance point and a  $0.001\mu IF$  to  $0.01\mu F$  ceramic capacitor should be connected from this pin to Common (pin 21) to prevent noise pickup. Refer to Figure 5 for relationship of Offset and Gain adjustments to unipolar and bipolar D/A operation.

FIGURE 5. Relationship of Offset and Gain Adjustments for a Unipolar and Bipolar D/A Converter.

#### **Offset Adjustment**

For unipolar (CSB) configurations, apply the digital input code that should produce zero potential output and adjust the Offset potentiometer for zero output.

For bipolar (COB, CTC) configurations, apply the digital input code that should produce the maximum negative output. Example: If the Full Scale Range is connected for 20V, the maximum negative output voltage is –10V. See Table II for corresponding codes.

#### **Gain Adjustment**

For either unipolar or bipolar configurations, apply the digital input that should give the maximum positive output. Adjust the Gain potentiometer for this positive full scale output. See Table II for positive full scale voltages and currents.

|                                                                                                                                                                                                                                       | ANALOG OUTPUT                                         |                                                        |                                                            |                                                           |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| DIGITAL INPUT                                                                                                                                                                                                                         | VOLTAGE <sup>(1)</sup>                                |                                                        | CURI                                                       | RENT                                                      |  |  |  |

| MSB LSB                                                                                                                                                                                                                               | 0 to +10V                                             | 0 to +10V ±10V                                         |                                                            | ±1mA                                                      |  |  |  |

| 0000000000000<br>011111111111<br>10000000000                                                                                                                                                                                          | +9.9976V<br>+5.0000V<br>+4.9976V<br>0.0000V<br>2.44mV | +9.9951V<br>0.0000V<br>-0.0049V<br>-10.0000V<br>4.88mV | -1.9995mA<br>-1.0000mA<br>-0.9995mA<br>0.0000mA<br>0.488µA | -0.9995mA<br>0.0000mA<br>+0.0005mA<br>+1.000mA<br>0.488µA |  |  |  |

| One LSB 2.44mV 4.88mV 0.488μA 0.488μA  NOTE: (1) To obtain values for other binary ranges: 0 to +5V range divide 0 to +10V range values by 2.  ±5V range: divide ±10V range values by 2.  ±2 5V range: divide ±10V range values by 4. |                                                       |                                                        |                                                            |                                                           |  |  |  |

TABLE II. Digital Input/Analog Output.

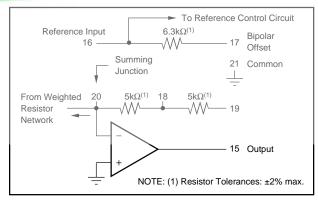

# **VOLTAGE OUTPUT MODELS Output Range Connections**

Internal scaling resistors provided in the DAC80 may be connected to produce bipolar output voltage ranges of  $\pm 10$ V,  $\pm 5$ V, or  $\pm 2.5$ V; or unipolar output voltage ranges of 0 to  $\pm 5$ V or 0 to  $\pm 10$ V. See Figure 6.

FIGURE 6. Output Amplifier Voltage Range Scaling Circuit.

Gain and offset drift are minimized because of the thermal tracking of the scaling resistors with other internal device components. Connections for various output voltage ranges are shown in Table III. Settling time for a full-scale range change is specified as  $4\mu s$  for the 20V range and  $3\mu s$  for the 10V range.

| Output<br>Range | Digital<br>Input Codes |    | Connect<br>Pin 17 to |    | Connect<br>Pin 16 to |

|-----------------|------------------------|----|----------------------|----|----------------------|

| ±10             | COB or CTC             | 19 | 20                   | 15 | 24                   |

| ±5              | COB or CTC             | 18 | 20                   | NC | 24                   |

| ±2.5V           | COB or CTC             | 18 | 20                   | 20 | 24                   |

| 0 to +10V       | CSB                    | 18 | 21                   | NC | 24                   |

| 0 to +5V        | CSB                    | 18 | 21                   | 20 | 24                   |

TABLE III. Output Voltage Range Connections for Voltage Models.

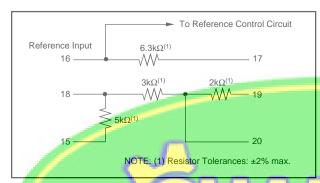

#### **CURRENT OUTPUT MODELS**

The resistive scaling network and equivalent output circuit of the current model differ from the voltage model and are shown in Figures 7 and 8.

FIGURE 7. Internal Scaling Resistors

FIGURE 8. Current Output Model Equivalent Output Circuit.

Internal scaling resistors (Figure 7) are provided to scale an external op amp or to configure load resistors for a voltage output. These connections are described in the following sections.

If the internal resistors are not used for voltage scaling, external  $R_L$  (or  $R_F$ ) resistors should have a TCR of  $\pm 25 ppm/^{\circ}C$  or less to minimize drift. This will typically add  $\pm 50 ppm/^{\circ}C$  plus the TCR of  $R_L$  (or  $R_F$ ) to the total drift.

#### **Driving An External Op Amp**

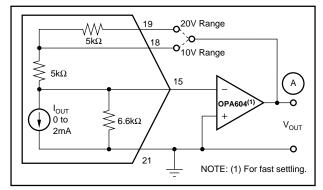

The current output model DAC80 will drive the summing junction of an op amp used as a current-to-voltage converter to produce an output voltage. See Figure 9.

$$V_{OUT} = I_{OUT} \times R_F$$

where  $I_{\text{OUT}}$  is the DAC80 output current and  $R_{\text{F}}$  is the feedback resistor. Using the internal feedback resistors of

FIGURE 9. External Op-Amp—Using Internal Feedback Resistors.

the current output model DAC80 provides output voltage ranges the same as the voltage model DAC80. To obtain the desired output voltage range when connecting an external op amp, refer to Table IV.

|   | Output<br>Range | Digital<br>Input Codes | Connect<br>A to | Connect<br>Pin 17 to | Connect<br>Pin 19 to | Connect<br>Pin 16 to |

|---|-----------------|------------------------|-----------------|----------------------|----------------------|----------------------|

| ı | ±10V            | COB or CTC             | 19              | 15                   | A                    | 24                   |

|   | ±5V             | COB or CTC             | 18              | 15                   | NC                   | 24                   |

|   | ±2.5V           | COB or CTC             | 18              | 15                   | 15                   | 24                   |

|   | 0 to +10V       | CSB                    | 18              | 21                   | NC                   | 24                   |

|   | 0 to +5V        | CSB                    | 18              | 21                   | 15                   | 24                   |

TABLE IV. Voltage Range of Current Output.

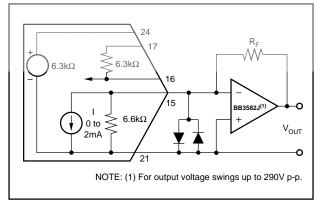

#### Output Larger Than 20V Range

For output voltage ranges larger than ±10V, a high voltage op amp may be employed with an external feedback resistor. Use I<sub>OUT</sub> value of ±1mA for bipolar voltage ranges and -2mA for unipolar voltage ranges. See Figure 10. Use protection diodes when a high voltage op amp is used.

The feedback resistor,  $R_F$ , should have a temperature coefficient as low as possible. Using an external feedback resistor, overall drift of the circuit increases due to the lack of temperature tracking between  $R_F$  and the internal scaling resistor network. This will typically add 50ppm/°C plus  $R_F$  drift to total drift.

FIGURE 10. External Op-Amp—Using External Feedback Resistors.

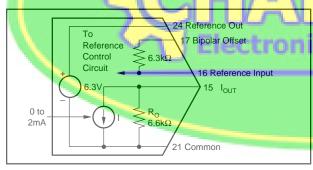

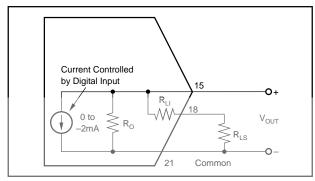

#### **Driving a Resistive Load Unipolar**

A load resistance,  $R_L = R_{LI} + R_{LS}$ , connected as shown in Figure 11 will generate a voltage range,  $V_{OUT}$ , determined by:

$$V_{OUT} = -2mA [(R_L \times R_O) \div (R_L + R_O)]$$

FIGURE 11. Current Output Model Equivalent Circuit Connected for Unipolar Voltage Output with Resistive Load.

The unipolar output impedance  $R_o$  equals  $6.6k\Omega$  (typ) and  $R_{LI}$  is the internal load resistance of  $968\Omega$  (derived by connecting pin 15 to 20 and pin 18 to 19). By choosing  $R_{LS} = 210\Omega$ ,  $R_L = 1178\Omega$ .  $R_L$  in parallel with  $R_o$  yields  $1k\Omega$  total load. This gives an output range of 0 to -2V. Since  $R_o$  is not exact, initial trimming per Figure 3 may be necessary; also  $R_{LS}$  may be trimmed.

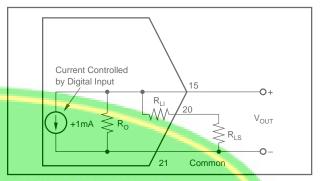

#### **Driving a Resistive Load Bipolar**

The equivalent output circuit for a bipolar output voltage range is shown in Figure 12,  $R_L = R_{LI} + R_{LS}$ .  $V_{OUT}$  is determined by:

$$V_{OUT} = \pm 1 \text{mA} [(R_0 \times R_1) \div (R_0 + R_1)]$$

By connecting pin 17 to 15, the output current becomes bipolar ( $\pm 1 \text{mA}$ ) and the output impedance  $R_0$  becomes  $3.2 \text{k}\Omega$  ( $6.6 \text{k}\Omega$  in parallel with  $6.3 \text{k}\Omega$ ).  $R_{LI}$  is  $1200\Omega$  (derived by connecting pin 15 to 18 and pin 18 to 19). By choosing  $R_{LS} = 225\Omega$ ,  $R_L = 1455\Omega$ .  $R_L$  in parallel with  $R_0$  yields  $1 \text{k}\Omega$  total load. This gives an output range of  $\pm 1 \text{V}$ . As indicated above, trimming may be necessary.

FIGURE 12. Current Output Model Connected for Bipolar Output Voltage with Resistive Load.

Electronics Group Co.,Ltd.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated