2429.5

| _ |                                                       |

|---|-------------------------------------------------------|

|   |                                                       |

|   |                                                       |

|   | PART WITHDRAWN                                        |

|   | WITHDRAWN                                             |

|   | PART WITHDRALE<br>PROCESS OBSOLETE<br>PROCESS DESIGNS |

|   | ACESS OBSULL                                          |

|   | PROCESS ODS<br>NO NEW DESIGNS                         |

|   | NEW DESIGN                                            |

|   | NUT                                                   |

### Features

- Maximum Rating...... 500V

- Ability to Interface and Drive Standard and Current Sensing N-Channel Power MOSFET/IGBT Devices

- Creation and Management of a Floating Power Supply for Upper Rail Drive

- Simultaneous Conduction Lockout

- Overcurrent Protection

- Single Low Current Bias Supply Operation

- Latch Immune CMOS Logic

- Peak Drive in Excess of 0.5A

File Number

## Half Bridge 500VDC Driver

July 1998

The SP601 is a smart power high voltage integrated circuit (HVIC) optimized to drive MOS gated power devices in halfbridge topologies. It provides the necessary control and management for PWM motor drive, power supply, and UPS applications.

# **Ordering Information**

| PART<br>NUMBER | TEMPERATURE<br>RANGE                     | PACKAGE             |

|----------------|------------------------------------------|---------------------|

| SP601          | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 22 Lead Plastic DIP |

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a registered trademark of Intersil Americas Inc. Copyright © Intersil Americas Inc. 2002. All Rights Reserved

| <b>Absolute Maximum Ratings</b> Full Temperature Range, All Voltage Referenced to V <sub>SS</sub> Unless Otherwise Noted. Note 1, Note 2.                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low Voltage Power Supply, V <sub>BIAS</sub> (Note 1)                                                                                                           |

| Low Voltage Signal Pins                                                                                                                                        |

| Fault, I <sub>TRIPSEL</sub> , V <sub>DD</sub> , TRIP <sub>L</sub> , CL1, G2L0.5V <sub>DC</sub> to V <sub>DD</sub> +0.5<br>G1L, D1L, V <sub>DF</sub> , TOP, BOT |

| CL2, TRIPU, G1U, G2U, D1U to Phase0.5 <sub>VDC</sub> to V <sub>BS</sub> +0.5                                                                                   |

| High Voltage Pins                                                                                                                                              |

| Phase, V <sub>PHASE</sub>                                                                                                                                      |

| Dynamic High Voltage Rating Phase,                                                                                                                             |

| NOTES:                                                                                                                                                         |

| 1. Care must be taken in the application of $V_{-1}$ - as not to impose high peak disc                                                                         |

### **Thermal Information**

| Thermal Resistance, Junction-to-Ambient                                    | θ <sub>JA</sub>         |

|----------------------------------------------------------------------------|-------------------------|

| Plastic DIP Package                                                        | 75 <sup>0</sup> C/W     |

| Maximum Package Power Dissipation at $T_A = +85^{\circ}C$ , P <sub>C</sub> | C                       |

| Plastic DIP Package                                                        | 500mW                   |

| Operating Ambient Temperature Range, T <sub>A</sub> 40 <sup>o</sup>        | C to +85 <sup>o</sup> C |

| Storage Temperature Range, T <sub>S</sub> 40 <sup>o</sup> C                | to +150 <sup>0</sup> C  |

| Lead Temperature (Soldering 10s)                                           | +265 <sup>0</sup> C     |

1. Care must be taken in the application of  $V_{BIAS}$  as not to impose high peak dissipation demands on a relatively small metallized noise dropping resistor ( $R_{ND}$ ). Prolonged high peak currents may result if +15 $V_{DC}$  is applied abruptly and/or if the local bypass capacitor  $C_{DD}$  is large. It is suggested that  $C_{DD}$  be  $\leq$  10MFD. If it is desirable to switch the 15 $V_{DC}$  source or if a  $C_{DD}$  is larger, additional series impedance may be required.

2. Consult factory for additional package offerings.

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

**Electrical Specifications** (V<sub>BIAS</sub> = 15V, Pulsed <300ms), Unless Otherwise Noted, All Parameters Referenced to V<sub>SS</sub> Except TRIP<sub>U</sub>, CL2, G1U, D1U, and V<sub>BS</sub> Referenced to PHASE. D<sub>F</sub>: V<sub>DF</sub> to V<sub>BS</sub>, C<sub>F</sub>: V<sub>BS</sub> to PHASE

| PARAMETER                                                                                                 | SYMBOL                 | TEMP                                     | MIN  | ТҮР  | MAX  | UNITS |

|-----------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------|------|------|------|-------|

| DC CHARACTERISTICS                                                                                        |                        |                                          |      |      |      |       |

| Input Current (5V < V <sub>TOP</sub> , V <sub>BOT</sub> , V <sub>TRIPSEL</sub> < 15V)                     | I <sub>IN</sub>        | +25 <sup>0</sup> C                       | -    | 20   | 30   | μA    |

|                                                                                                           |                        | -40 <sup>o</sup> C to +85 <sup>o</sup> C | -    | 30   | 33   | μΑ    |

| IBIAS Quiescent Current (All Inputs Low)                                                                  | IBIASL                 | +25 <sup>0</sup> C                       | -    | 1.7  | 2.05 | mA    |

|                                                                                                           |                        | -40 <sup>o</sup> C to +85 <sup>o</sup> C | -    | 1.7  | 2.1  | mA    |

| IBIAS Quiescent Current                                                                                   | I <sub>BIASH</sub>     | +25 <sup>0</sup> C                       | -    | 1.7  | 2.05 | mA    |

| $(V_{OUT} \ge V_{BIAS}, and All Inputs Low)$                                                              |                        | -40 <sup>o</sup> C to +85 <sup>o</sup> C | -    | 1.7  | 2.1  | mA    |

| IBS Quiescent Current Bootstrap Supply                                                                    | I <sub>BS</sub>        | +25 <sup>0</sup> C                       | -    | 875  | 1000 | μΑ    |

|                                                                                                           |                        | -40 <sup>o</sup> C to +85 <sup>o</sup> C | -    | 900  | 1060 | μΑ    |

| ENABLE Threshold Level                                                                                    | V <sub>TOP</sub>       | +25 <sup>0</sup> C                       | 7    | 8    | 9    | V     |

|                                                                                                           |                        | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 6.95 | 8    | 9.1  | V     |

| UP/DN Threshold Level                                                                                     | V <sub>BOT</sub>       | +25 <sup>0</sup> C                       | 7    | 8    | 9    | V     |

|                                                                                                           |                        | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 6.95 | 8    | 9.1  | V     |

| Current Trip Select Threshold Level                                                                       | V <sub>TRIPSEL</sub>   | +25 <sup>0</sup> C                       | 7    | 8    | 9    | V     |

|                                                                                                           |                        | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 6.95 | 8    | 9.1  | V     |

| Trip Lower and Upper Comparator Threshold                                                                 | V <sub>TRIP L/UN</sub> | +25 <sup>0</sup> C                       | 90   | 105  | 125  | mV    |

| Level - Normal (I <sub>TRIPSEL</sub> = V <sub>SS</sub> )                                                  |                        | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 90   | 105  | 127  | mV    |

| Trip Lower and Upper Comparator Threshold                                                                 | V <sub>TRIP L/UB</sub> | +25 <sup>0</sup> C                       | 110  | 130  | 150  | %     |

| Level - Boost (I <sub>TRIPSEL</sub> = V <sub>DD</sub> ) % of Measured V <sub>TRIP L</sub> /U <sub>N</sub> |                        | -40°C to +85°C                           | 109  | 130  | 152  | %     |

| Under Voltage Lockout Thresholds (V_DD and V_BS)                                                          | V <sub>LOCK</sub>      | +25 <sup>0</sup> C                       | 9    | 10   | 11.5 | V     |

|                                                                                                           |                        | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 9.7  | 10.5 | 11.8 | V     |

| Phase Out of Status Voltage Threshold (PHASE)                                                             | V <sub>OSVT</sub>      | +25 <sup>0</sup> C                       | 5    | 7    | 9    | V     |

|                                                                                                           |                        | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 4.7  | 7    | 9.6  | V     |

| Faultbar Impedance at I <sub>FBAR</sub> = 1mA                                                             | RF                     | +25 <sup>0</sup> C                       | 500  | 760  | 1000 | Ω     |

|                                                                                                           |                        | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 450  | 760  | 1100 | Ω     |

|                                                                                                                          | 20                          | 1 51                                     | 50 1 | 20   |      |       |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------|------|------|------|-------|

| PARAMETER                                                                                                                | SYMBOL                      | ТЕМР                                     | MIN  | ТҮР  | MAX  | UNITS |

| Upper/Lower Source Impedances (I <sub>SOURCE</sub> = 10mA)                                                               | R <sub>SO L/U</sub>         | +25 <sup>0</sup> C                       | 12   | 17   | 23   | Ω     |

|                                                                                                                          |                             | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 7    | 17   | 29   | Ω     |

| Upper/Lower Sink Impedances (I <sub>SINK</sub> = 10mA)                                                                   | R <sub>SI L/U</sub>         | +25 <sup>0</sup> C                       | 8    | 12   | 16   | Ω     |

|                                                                                                                          |                             | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 5    | 12   | 20   | Ω     |

| Bootstrap Supply Current Limiting Impedance                                                                              | R <sub>BS</sub>             | +25 <sup>o</sup> C                       | 2    | 3.5  | 5    | Ω     |

|                                                                                                                          |                             | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 1.4  | 3.5  | 5.6  | Ω     |

| Noise Dropping Resistor Impedance                                                                                        | R <sub>ND</sub>             | +25 <sup>0</sup> C                       | 6    | 10   | 14   | Ω     |

|                                                                                                                          |                             | -40°C to +85°C                           | 5.4  | 10   | 14.6 | Ω     |

| High Voltage Leakage (500V $V_{BS}, V_{OUT}, PHASE, TRIP_U, CL2, G1U, G2U, and D1U to V_{SS}. All other Pins at V_{SS})$ | Ι <sub>LK</sub>             | +25 <sup>o</sup> C                       | -    | 1    | 3    | μΑ    |

| Miller Clamp Diodes; D1U and D1L ( $I_D = 10mA$ )                                                                        | V <sub>D1U/L</sub>          | +25 <sup>0</sup> C                       | 0.4  | 0.9  | 1.4  | V     |

| Noise Clamping Zeners; CL2 and CL1 ( $I_Z = 10mA$ )                                                                      | V <sub>CL2/1-LOW</sub>      | +25°C                                    | 6.35 | 6.61 | 6.85 | V     |

|                                                                                                                          |                             | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 6.15 | 6.61 | 7.15 | V     |

| Noise Clamping Zeners; CL2 and CL1 ( $I_Z = 50mA$ )                                                                      | V <sub>CL2/1-</sub><br>HIGH | +25 <sup>o</sup> C                       | 7.0  | 8.5  | 8.0  | V     |

| V <sub>OUT</sub> Limiting Resistance                                                                                     | R <sub>O</sub>              | +25 <sup>o</sup> C                       | 2    | 3.5  | 5    | Ω     |

|                                                                                                                          |                             | -40 <sup>o</sup> C to +85 <sup>o</sup> C | 1.4  | 3.5  | 5.6  | Ω     |

$\begin{array}{l} \textbf{Electrical Specifications} \\ (V_{BIAS} = 15V, \mbox{Pulsed <300ms}), \mbox{Unless Otherwise Noted}, \mbox{All Parameters Referenced to V}_{SS} \mbox{Except TRIP}_{U}, \\ CL2, \mbox{G1U}, \mbox{D1U}, \mbox{and V}_{BS} \mbox{Referenced to PHASE}. \mbox{D}_{F}: \mbox{V}_{DF} \mbox{to V}_{BS}, \mbox{C}_{F}: \mbox{V}_{BS} \mbox{to PHASE} \mbox{(Continued)} \end{array}$

NOTE: Maximum Steady State  $\div$  15V<sub>DC</sub> Supply Current = I<sub>BIASL</sub>  $\div$  I<sub>BS</sub>

####

| PARAMETER                                                    | SYMBOL                         | ТЕМР               | MIN  | ТҮР | MAX  | UNITS |

|--------------------------------------------------------------|--------------------------------|--------------------|------|-----|------|-------|

| Refresh One Shot Timer                                       | t <sub>REF</sub>               | +25 <sup>0</sup> C | 200  | 350 | 500  | μs    |

|                                                              |                                | -40°C to +85°C     | 180  | 350 | 540  | μs    |

| Delay Time of Trip I/U Voltage (I <sub>TRIPSEL</sub> low) to | <sup>t</sup> OFF <sub>TN</sub> | +25 <sup>o</sup> C | 2    | 3   | 4    | μs    |

| G2U/G2L Low (50% Overdrive                                   |                                | -40°C to +85°C     | 1.85 | 3   | 4.35 | μs    |

| Delay Time of Trip I Voltage (I <sub>TRIPSEL</sub> low) to   | t <sub>FN</sub>                | +25 <sup>o</sup> C | 2    | 3   | 4    | μs    |

| Faultbar Low                                                 |                                | -40°C to +85°C     | 1.85 | 3   | 4.35 | μs    |

| Delay Time of Phase Out of Status to Faultbar                | <sup>t</sup> OSVF              | +25 <sup>0</sup> C | 500  | 700 | 900  | ns    |

| Low (TOP High)                                               |                                | -40°C to +85°C     | 400  | 700 | 1050 | ns    |

| Minimum Logic Input Pulse Width: TOP and                     | t <sub>MINIW</sub>             | +25 <sup>0</sup> C | 300  | 430 | 600  | ns    |

| BOTTOM                                                       |                                | -40°C to +85°C     | 275  | 430 | 660  | ns    |

| Minimum G1U/G1L On Time                                      | t <sub>ON</sub>                | +25 <sup>0</sup> C | 1.6  | 2.3 | 3.1  | μs    |

|                                                              |                                | -40°C to +85°C     | 1.5  | 2.4 | 3.4  | μs    |

| Minimum Pulsed Off Time, G2U/G2L                             | <sup>t</sup> OFF               | +25 <sup>0</sup> C | 1.3  | 2.0 | 3.4  | μs    |

|                                                              |                                | -40°C to +85°C     | 1.05 | 2.1 | 3.9  | μs    |

| Turn On Delay Time of G1U (BISTATE MODE)                     | t <sub>OND</sub>               | +25 <sup>0</sup> C | 2.5  | 3.2 | 4.5  | μs    |

|                                                              |                                | -40°C to +85°C     | 2.1  | 3.3 | 5.2  | μs    |

| Turn On Delay Time of G1L (BISTATE MODE)                     | t <sub>OND</sub>               | +25 <sup>0</sup> C | 2.5  | 3.2 | 4.5  | μs    |

|                                                              | _                              | -40°C to +85°C     | 2.1  | 3.3 | 5.2  | μs    |

| Turn On Delay Time of G1U                                    | t <sub>OND</sub>               | +25 <sup>0</sup> C | 0.75 | 1.0 | 1.5  | μs    |

| (THREE-STATE MODE)                                           | _                              | -40°C to +85°C     | 0.60 | 1.1 | 1.75 | μs    |

| PARAMETER                                | SYMBOL                        | TEMP               | MIN  | ТҮР | МАХ  | UNITS |

|------------------------------------------|-------------------------------|--------------------|------|-----|------|-------|

| Turn On Delay Time of G1L                | t <sub>OND</sub>              | +25 <sup>0</sup> C | 0.75 | 1.0 | 1.5  | μs    |

| (THREE-STATE MODE)                       |                               | -40°C to +85°C     | 0.60 | 1.1 | 1.75 | μs    |

| Turn Off Delay Time of G2U and G2L       | <sup>t</sup> OFF <sub>D</sub> | +25 <sup>0</sup> C | 0.75 | 1.0 | 1.45 | μs    |

|                                          |                               | -40°C to +85°C     | 0.60 | 1.1 | 1.75 | μs    |

| Minimum Dead Time: G1U OFF to G1L ON, or | <sup>t</sup> D.T.             | +25 <sup>0</sup> C | 1.5  | 2.5 | 3.5  | μs    |

| G1L off to G1U on (BISTATE MODE)         |                               | -40°C to +85°C     | 1.2  | 2.6 | 4    | μs    |

| Fault Reset Delay to Clear Faultbar      | <sup>t</sup> R.T.             | +25 <sup>0</sup> C | 3.4  | 4.5 | 6.6  | μs    |

|                                          |                               | -40°C to +85°C     | 3.15 | 4.8 | 7.4  | μs    |

| Rise Time of Upper and Lower Driver      | <sup>t</sup> R U/L            | +25 <sup>0</sup> C | 25   | 50  | 100  | ns    |

| (Load = 2000pF)                          |                               | -40°C to +85°C     | 15   | 50  | 115  | ns    |

| Fall Time of Upper and Lower Driver      | <sup>t</sup> F U/L            | +25 <sup>0</sup> C | 25   | 50  | 100  | ns    |

| (Load = 2000pF)                          |                               | -40°C to +85°C     | 15   | 50  | 115  | ns    |

#

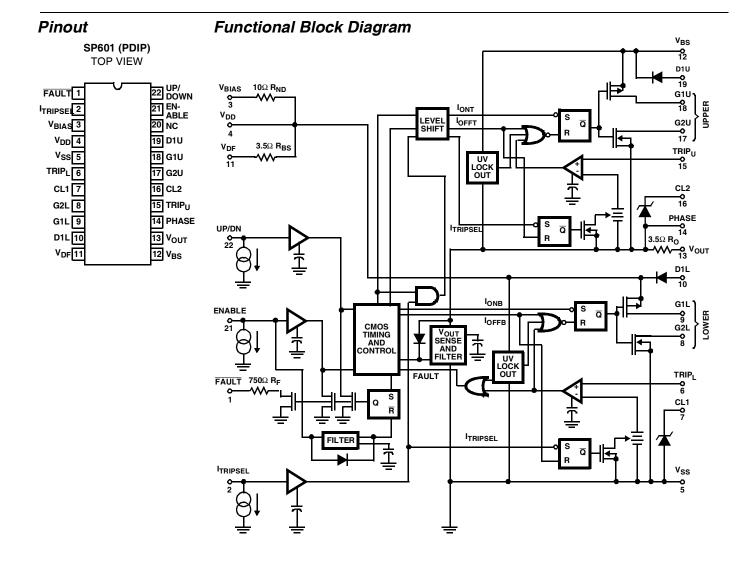

# Recommended Operating Conditions and Functional Pin Description (All Voltages Referenced to V<sub>SS</sub>, Unless Otherwise Noted. See Figure 1)

| PARAMETER         | CONDITION                                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------|

| FAULTBAR          | Open Drain Fault Indicator Output                                                                           |

| ITRIPSELECT       | Digital Input Command to Increase TRIPL and TRIPU Threshold by 30%                                          |

| V <sub>BIAS</sub> | 14.5V to 16.5V with 15V nominal, $\cong$ 1.5mA DC BIAS Current                                              |

| V <sub>DD</sub>   | C <sub>DD</sub> to V <sub>SS</sub>                                                                          |

| V <sub>SS</sub>   | COMMON                                                                                                      |

| TRIP I            | 100mV Signal to Shut Off LOWER Drive and Trigger a Fault Output                                             |

| CL1               | Lower Noise Clamp Zener                                                                                     |

| G2L and G1L       | Low Impedance Driver Designed to Drive Power MOS Transistors (LOWER)                                        |

| V <sub>DF</sub>   | Current Limiting Charging Resistor for Bootstrap Capacitor Power Supply                                     |

| V <sub>BS</sub>   | Bootstrap Supply, Normally a Diode Drop Below $V_{DD}$ Voltage with Respect to the Floating PHASE Reference |

| V <sub>OUT</sub>  | Load Connection Node                                                                                        |

| PHASE             | Floating Reference Point for High Side Control Circuitry: VBS, TRIPU, CL2, G1U, G2U and D1U                 |

| TRIPU             | 100mV Signal, Referenced to PHASE, to Shut Off UPPER Drive                                                  |

| CL2               | Upper Noise Clamp Zener                                                                                     |

| G2U and G1U       | Low Impedance Driver Designed to Drive Power MOS Transistors (UPPER)                                        |

| ENABLE            | Digital Input to ENABLE the UP/DN Command to Turn on Top/Bottom Devices                                     |

| UP/DN             | Digital Input to Top/Bottom Device (If ENABLE is High)                                                      |

| D1U               | Miller Clamp UPPER to V <sub>BS</sub>                                                                       |

| D1L               | Miller Clamp LOWER to V <sub>DD</sub>                                                                       |

4

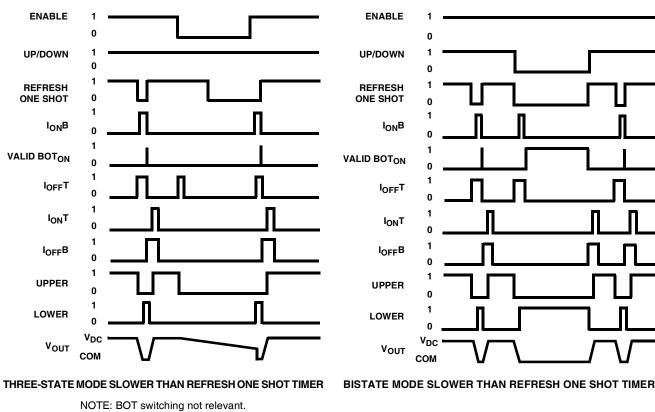

# Timing Diagram

BISTATE MODE SLOWER THAN REFRESH ONE SHOT TIMER

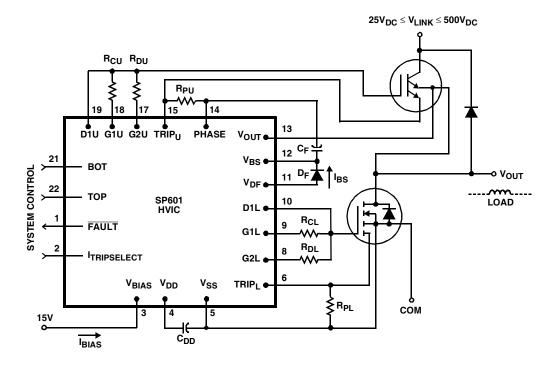

# Typical Circuit Configuration

|       |        | INP   | OUTPUTS |       |                   |       |       |           |

|-------|--------|-------|---------|-------|-------------------|-------|-------|-----------|

| UP/DN | ENABLE | TRIPL | TRIPU   | PHASE | V <sub>BIAS</sub> | UPPER | LOWER | FAULT BAR |

| 0     | 0      | 0     | Х       | Х     | 1                 | 0     | 0     | 1         |

| 1     | 1      | 0     | 0       | 1     | 1                 | 1     | 0     | 1         |

| 1     | 1      | 0     | 1       | 1     | 1                 | 0     | 0     | 0         |

| 1     | 1      | 0     | х       | 0     | 1                 | 0     | 0     | 0         |

| Х     | х      | 1     | х       | х     | 1                 | 0     | 0     | 0         |

| 0     | 1      | 0     | х       | х     | 1                 | 0     | 1     | 1         |

| 1     | 0      | 0     | х       | х     | 1                 | 0     | 0     | 1         |

| х     | х      | Х     | Х       | х     | 0                 | 0     | 0     | 0         |

**TRUTH TABLE** Applicable to Typical Circuit Configuration (Figure 1)

NOTE: 0 = False, 1 = True, X = Don't Care

| LEGEND                                                  |                 |                                       |  |  |  |  |

|---------------------------------------------------------|-----------------|---------------------------------------|--|--|--|--|

| Application Specific                                    | R <sub>CU</sub> | Upper Gate Charging Resistor          |  |  |  |  |

| Application Specific                                    | R <sub>DU</sub> | Upper Gate Discharge Resistor         |  |  |  |  |

| Application Specific                                    | R <sub>PU</sub> | Upper Current Pilot Resistor          |  |  |  |  |

| Application Specific                                    | R <sub>CL</sub> | Lower Gate Charging Resistor          |  |  |  |  |

| Application Specific                                    | R <sub>DL</sub> | Lower Gate Discharging Resistor       |  |  |  |  |

| Application Specific                                    | R <sub>PL</sub> | Lower Current Pilot Resistor          |  |  |  |  |

| 3μF at ≥ 15DC                                           | C <sub>DD</sub> | Local LV Filter Capacitor             |  |  |  |  |

| $0.22\mu F$ Ceramic X7R at $\ge 15V_{DC}$               | C <sub>F</sub>  | Flying Capacitor for Bootstrap Supply |  |  |  |  |

| Intersil P/N A114M or Equiv PRV $\ge$ V <sub>LINK</sub> | D <sub>F</sub>  | Flying Diode for Bootstrap Supply     |  |  |  |  |

NOTE: Refer to 'Additional Product Offerings' for information concerning power output devices.

The SP601 provides a flexible, digitally controlled power function which is intended to be used as PWM drivers of N-Channel MOSFETs and/or IGBTs for up to 240VAC line rectified totem-pole applications. The CMOS driveable inputs are filtered and captured by the control logic to determine the output state. The logic includes fixed timing to prohibit simultaneous conduction of the external power switches and, thru the VOUT sense detector, verifies the output voltage state is in agreement with the controlled inputs. The  $> 11V_{DC}$  floating power supply required to drive the upper rail external power device is created and managed by the HVIC through C<sub>F</sub> and D<sub>F</sub>. This capacitor is refreshed from the V<sub>DD</sub> supply each time V<sub>OUT</sub> goes low. If the upper channel is commanded on for a long period of time, the bootstrap capacitor C<sub>F</sub> is automatically refreshed by bringing V<sub>OUT</sub> low. This is accomplished by turning off the upper rail MOS-FET/IGBT, momentarily turning on the lower rail output device, followed by returning control back to the upper switch. Otherwise, CF would gradually deplete its charge allowing the upper switch to come out of saturation. The upper and lower gate drivers allow for controlled charge and discharge rates as well as facilitate the use of nearly lossless current sensing power MOS devices. The over current trip level can be boosted 30% on a pulse by pulse basis by logic level '1' applied to ITRIPSELECT. A FAULT output signal is generated when any of the following occurs:

V bias is low Over current is detected V phase doesn't agree with the input signal

Reset of  $\overline{FAULT}$  is provided by externally removing power or by holding the ENABLE input low for the required reset time (trt<sub>MAX</sub>).

Each application can be individually optimized by the selection of external components tailored to ensure proper overall system operation including:

Determining the ratings and sizing of MOSFETs and IGBTs, mixed or matched, as well as flyback diodes (FBD).

The selection of separate gate charge ( $R_C$ ) and discharge ( $R_D$ ) impedance chosen per the load capacitance, frequency of operation, and  $D_I/D_T$  dependent recovery characteristics of the associated FBDs.  $R_D$  should also be sized to prevent simultaneous bridge conduction by ensuring gate discharge in the allotted turn off pulse width ( $t_{OFF MIN}$ ).

The selection of over current detection resistors ( $R_P$ ), compatible with current sense MOSFETs/IGBTs or shunt(s) may be used.

For the floating bootstrap supply D<sub>F</sub> and C<sub>F</sub> must be determined. D<sub>F</sub> must support the worse case system bus voltage and handle the charging currents of C<sub>F</sub>. Proper selection should take into consideration T<sub>RR</sub> and T<sub>FR</sub> per the desired operating frequency. Proper selection of C<sub>F</sub> is a trade off between the minimum t<sub>ON</sub> time of the lower rail to charge up the capacitor, the amount of charge transfer required by the load, and cost. Due to automatic refresh the capacitor is replenished every 350µs TYP (or even sooner if the UP/DN input switches at a faster repetition rate).

The local filter capacitor (C<sub>DD</sub>) should be sized sufficiently large enough to transfer the charge to C<sub>F</sub> without causing a significant droop in V<sub>DD</sub>. As a rule of thumb it should be at least 10 times larger than C<sub>F</sub> and be located adjacent to the V<sub>DD</sub> and V<sub>SS</sub> pins to minimize series resistance and inductance.

Refer to Application Note AN8829 for more details about module operation and selection of external components.