TOSHIBA TA7900S/F

TOSHIBA BIPOLAR LINEAR INTEGRATED CIRCUIT SILICON MONOLITHIC

# **TA7900S, TA7900F**

# **5V VOLTAGE REGULATOR WITH WATCHDOG TIMER**

The TA7900S, TA7900F is an IC specially designed for micro-computer systems. It produces an output voltage of  $5\pm0.25V$  without need for adjustment from its accurate reference voltage and amplifier circuit.

At power-on, it outputs a reset signal to reset the system. It will also output a reset signal when the 5V output voltage drops below 92% because of external disturbance or other problem. It also incorporates a watchdog timer for self-diagnosing the system. When the system malfunctions, the IC generates reset pulses intermittently to prevent the system from running away.

### **FEATURES**

Accurate output : 5 ± 0.25V

Output voltage adjusting pin attached

Power-on reset timer incorporated

Watchdog timer incorporated

Operating temperature range : from -40 to 85°C

Wide operating voltage range : 40V (max.)

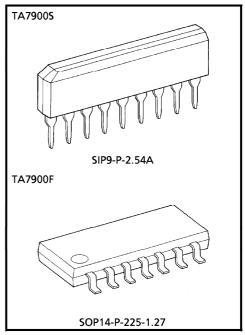

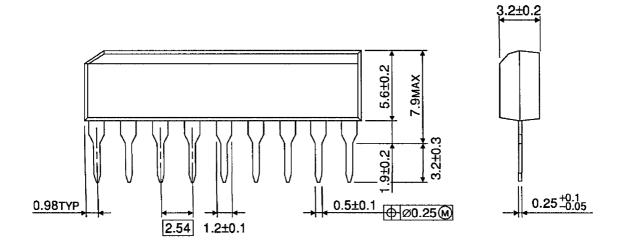

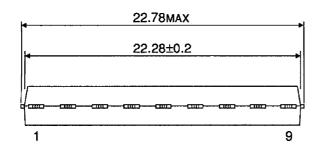

Small SIP-9 pin (TA7900S)

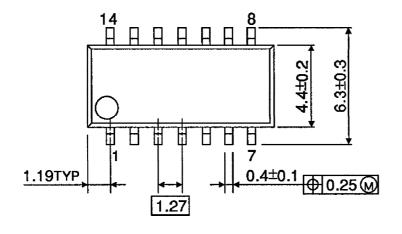

• SOP-14 pin (TA7900F)

Weight

SIP9-P-2.54A : 0.92g (Typ.) SOP14-P-225-1.27 : 0.2g (Typ.)

980910EBA1

■ The products described in this document are subject to the foreign exchange and foreign trade laws.

■ The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

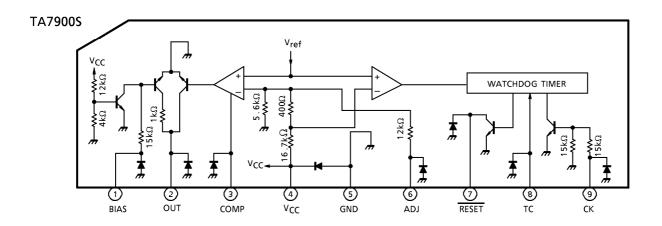

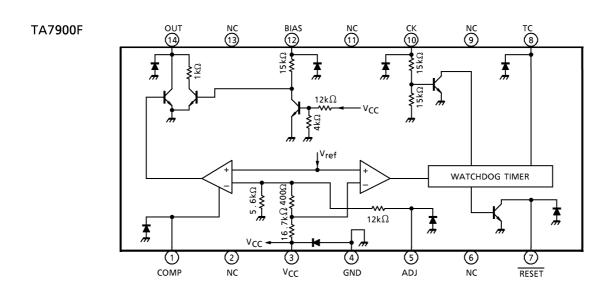

# **BLOCK DIAGRAM AND PIN LAYOUT**

Note: The TA7900S and TA7900F are the same chip, except that they are housed in different packages.

# PIN DESCRIPTION

| PIN No. |                    | SYMBOL          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|---------|--------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TA7900S | TA7900F            | STIVIBOL        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 1       | 12                 | BIAS            | Power supply starting pin. The starting current is supplied through a resistor to which the input voltage is applied. The output current from this starting current is as follows : $I_{OUT} (\text{BIAS PIN}) \geq 30 \times (V_{IN} - 0.7) / (15 + R_1)  (\text{mA}) \\ \text{where } R_1 \text{ is the external resistance attached to BIAS pin } (k\Omega)  .$ When $V_{CC}$ rises above 2.7V, the starting current is absorbed in the internal circuit; instead, $I_{OUT}$ is supplied via $V_{CC}$ . |  |  |

| 2       | 14                 | оит             | Connected to the base of an external PNP transistor so that the output voltage is stabilized. Power supply design suitable for particular load capacities is thus possible.  Since the recommended maximum IOUT is 5mA, an output current of 300mA is assured if the external transistor has an HFE of 60 or more.                                                                                                                                                                                         |  |  |

| 3       | 1                  | COMP            | Phase compensation pin for output stabilization                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 4       | 3                  | V <sub>CC</sub> | Power supply pin for internal circuit. The output voltage can also be detected at this pin.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 5       | 4                  | GND             | Grounded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

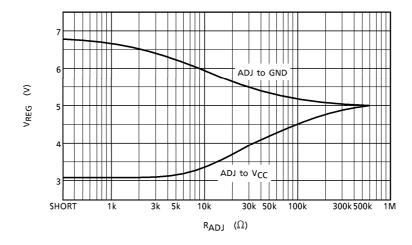

| 6       | 5                  | ADJ             | Output voltage adjust pin. The voltage can be raised by inserting a resistor between GND and this pin and can be lowered by inserting a resistor between V <sub>CC</sub> and this pin. The voltage can be adjusted more or less ± 1V in this way.                                                                                                                                                                                                                                                          |  |  |

| 7       | 7                  | RESET           | <ul> <li>NPN transistor open-collector output.</li> <li>(1) The signal goes low when the output drops below 92% of the specified level.</li> <li>(2) The pin supplies a reset signal determined by the CR combination connected to the TC pin.</li> <li>(3) The pin supplies reset pulses intermittently if no clock is given to the CK pin. This function is useful when the IC is used as a watchdog timer for a microcomputer system.</li> </ul>                                                        |  |  |

| 8       | 8                  | TC              | This pin is used to set the time on the reset timer and watchdog timer. The time can be set using an external $C_T$ and $R_T$ .                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 9       | 10                 | СК              | Input pin for watchdog timer. The pin is pulled up to $V_{CC}$ if the IC is used only as a power-on reset timer.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|         | 2, 6, 9,<br>11, 13 | NC              | Not connected. (This pin electrically is completely open.)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

TOSHIBA

### **Functional Description**

The TA7900S/F contains a 5V constant-voltage power supply function to feed a stable power supply voltage to the CPU, etc., and a system reset function to ensure a stable operation of the CPU, etc. These functions are explained below.

#### (1) 5V constant-voltage power supply function

This function has a reference voltage Vref within the IC that is unaffected by temperature and input voltage changes. This voltage is stepped up to 5V by using an op-amp and dividing resistor. These op-amp and dividing resistor plus the output transistor connected to the op-amp's output configure a closed loop.

When using only the reset timer without using this power supply function, be sure to connect the BIAS OUT COMP pin to GND.

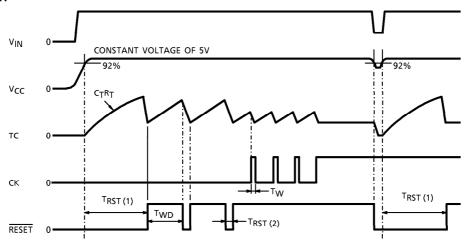

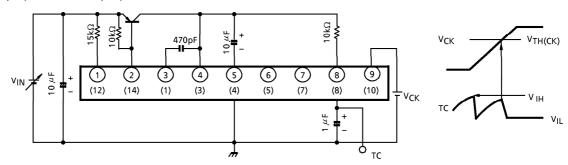

# (2) System reset function (See the timing chart)

#### (2-1) Voltage monitoring function

If the voltage Vcc applied to the CPU exceeds 4.6V when powered on, the power-on reset timer starts from that point in time. If the Vcc drops below 4.6V when powered off, a reset signal is output immediately. Also, when the  $V_{CC}$  drops for some reason under normal operating condition, a reset signal is output immediately, and when the  $V_{CC}$  exceeds 4.6V after being restored to the normal voltage, the power-on reset timer starts from that point in time.

#### (2-2) Power-on reset timer function

The reset signal is deasserted after holding the device in a reset state for a predetermined time until the 5V constant voltage stabilizes at power-on time or until the oscillating clock fed to the CPU, etc. stabilizes. This duration of time can be set as desired by choosing the values of the external resistor and capacitor connected to the TC pin. When the V<sub>CC</sub> voltage exceeds 4.6V, current is sourced to start charging the capacitor and when this charge voltage exceeds 4V, the capacitor is discharged by the internal transistor. When the capacitor has been discharged to a voltage of 2V, the reset signal is inverted to deactivate the reset.

#### (2-3) Watchdog timer function

Program the CPU system software to output a clock each time one program routine is completed and enter this clock to the device's CK pin. Although the TC pin of the device repeatedly charges and discharges between 2V and 4V, when a clock pulse is applied, it switches to discharging in the middle of charging and starts charging from 2V again. Since when the CPU system is operating normally the clock is generated at predetermined intervals, the pin switches to discharging before the charge voltage reaches 4V. However, if no clock is applied while charging from 2V to 4V, it is assumed that the clock has been interrupted, i.e., the CPU system has gone wild, thus generating a reset signal to reset the CPU system. The CPU system and the device's CK pin are connected with a differentiating circuit. This is to ensure that even in the event the CPU system goes wrong, the CK pin is always fed with a low-level clock regardless of whether the clock output has stopped in the high or low state. If the CK pin is fixed high, no reset signal is output, in which case only the power-on reset timer operates.

### **TIMING CHART**

(Note)  $T_{RST\,(1)},\,T_{RST\,(2)},\,T_{WD},\,T_{W}$  : See Attached Electrical Characteristics.

# MAXIMUM RATINGS (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL            | RATING      | UNIT     |

|-----------------------|-------------------|-------------|----------|

| Input Valtage         | V <sub>IN1</sub>  | 40          | V        |

| Input Voltage         | V <sub>IN2</sub>  | -0.3 to +16 | >        |

| Output Current        | lOUT1             | 10          | mΑ       |

| Curput Current        | IOUT2             | 4           | ША       |

| Output Voltage        | V <sub>OUT1</sub> | 40          | V        |

| Output Voltage        | V <sub>OUT2</sub> | 16          | <b>V</b> |

| Power Dissipation     | PD                | 500 / 280   | mW       |

| Operating Temperature | T <sub>opr</sub>  | -40 to 85   | °C       |

| Storage Temperature   | T <sub>stg</sub>  | - 55 to 150 | °C       |

| Lead Temperature-time | T <sub>sol</sub>  | 260 (10s)   | °C       |

V<sub>IN1</sub> : BIAS input

V<sub>IN2</sub> : CK input

I<sub>OUT1</sub>, V<sub>OUT1</sub> : OUT output

I<sub>OUT2</sub>, V<sub>OUT2</sub> : RESET output

P<sub>D</sub> : TA7900S / TA7900F

TOSHIBA TA7900S/F

**ELECTRICAL CHARACTERISTICS** ( $V_{IN} = 7$  to 17V, Ta = -40 to 85°C)

|                         |                                    | _      |                      |                               |                               |           |                |         |

|-------------------------|------------------------------------|--------|----------------------|-------------------------------|-------------------------------|-----------|----------------|---------|

| CHARACTERISTIC          | SYMBOL                             | PIN    | TEST<br>CIR-<br>CUIT | TEST CONDITION                | MIN.                          | TYP.      | MAX.           | UNIT    |

| Output Voltage          | V <sub>REG</sub>                   | Vcc    | 1                    | _                             | 4.75                          | 5.0       | 5.25           | V       |

| Line Regulation         | _                                  | ۷cc    | _                    | V <sub>IN</sub> = 7 to 40V    | -                             | 0.1       | 0.5            | %       |

| Load Regulation         | _                                  | ۷cc    | _                    | I <sub>LOAD</sub> = 1 to 50mA | -                             | 0.1       | 0.5            | %       |

| Temperature Coefficient | _                                  | Vcc    | _                    | _                             | -                             | 0.01      | _              | % /°C   |

| Output Voltage          | VOL                                | RESET  | 2                    | I <sub>OL</sub> = 2mA         | _                             | _         | 0.5            | ٧       |

| Output Leakage Current  | ILEAK                              | RESET  | 3                    | V <sub>OUT</sub> = 10V        | _                             | _         | 5              | μΑ      |

| Input Current           | IN                                 | TC     | 4                    | V <sub>IN</sub> = 0 to 3.5V   | - 3                           | _         | 3              | $\mu$ A |

| Threshold Voltage       | VIH                                | TC     | 5                    | RESET "High" to "Low"         |                               | 80% ×     |                | · V     |

|                         |                                    |        |                      | INCIDENT THIGHT TO LOW        |                               | $V_{REG}$ | _              |         |

| Threshold voltage       | V <sub>IL</sub>                    |        |                      | RESET "Low" to "High"         | _                             | 40% ×     |                |         |

|                         |                                    |        |                      |                               |                               | $V_{REG}$ | _              |         |

| Input Current           | I <sub>IN</sub>                    | CK     | 6                    | V <sub>IN</sub> = 5V          | _                             | 0.3       | 0.7            | mA      |

| Input Voltage           | V <sub>IH</sub><br>V <sub>IL</sub> | СК     | 5                    | _                             | 2                             | _         | 0.5 V          |         |

| input voitage           |                                    |        |                      | _                             | _                             |           |                |         |

| Reset Detect Voltage    | _                                  | Vcc    | _                    |                               | 89% ×                         | 92% ×     | 95% ×          | V       |

| _                       |                                    |        |                      | _                             | V <sub>REG</sub>              | $V_{REG}$ | $V_{REG}$      |         |

| Standby Current         | Is                                 | Vcc    | 8                    | V <sub>IN</sub> = 14V         | _                             | 5         | 6.5            | mA      |

| Watchdog Timer          | TWD                                | RESET  | 7                    |                               | 0.9×                          | 1.1 ×     | 1.3 ×          |         |

| Wateria og Tiller       | TWD                                | INL3L1 |                      | <del>-</del>                  | C <sub>T</sub> R <sub>T</sub> | $C_TR_T$  | $C_TR_T$       | ms      |

| Reset Timer (1)         | T <sub>RST (1)</sub> R             | RESET  | RESET 7              |                               | 1.3 ×                         | 1.6×      | 1.9×           |         |

| Reser Timer (1)         |                                    | IVESEI |                      | _                             | C <sub>T</sub> R <sub>T</sub> | CTRT      | $C_TR_T$       |         |

| Reset Timer (2)         | TDCT (2)                           | RESET  | 7                    |                               | 0.15×                         | 0.3×      | 0.6×           |         |

|                         | T <sub>RST</sub> (2)               |        |                      | _                             | C <sub>T</sub>                | CT        | C <sub>T</sub> |         |

| Clock Pulse Width       | TW                                 | CK     | <u> </u>             | _                             | 3                             |           | _              | $\mu$ s |

Note: Reset timer (1) : Power-on reset time

Reset timer (2) : Watchdog reset time

Reset timer (2) : Watchdog reset time The unit of  $\mathbf{C_T}$  is  $\mu\mathbf{F}$  : the unit of  $\mathbf{R_T}$  is  $\mathbf{k}\Omega$ .

**TOSHIBA**

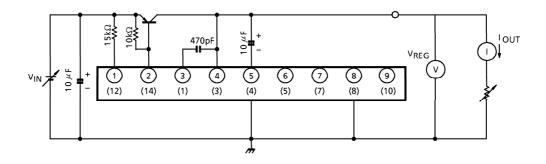

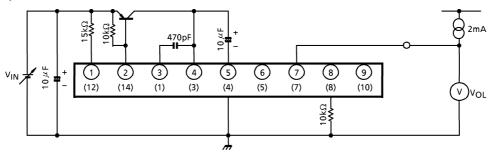

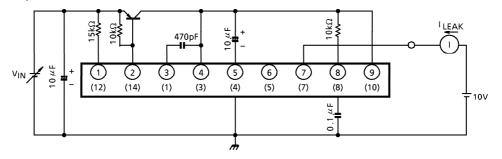

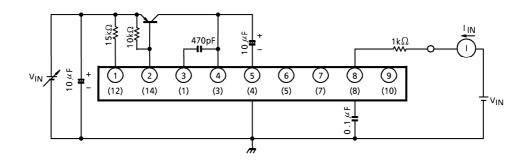

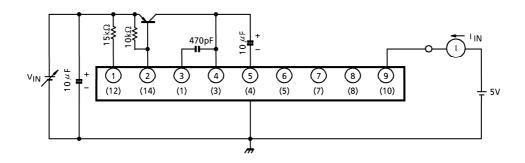

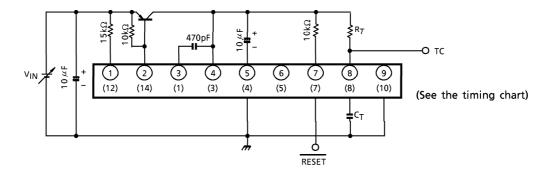

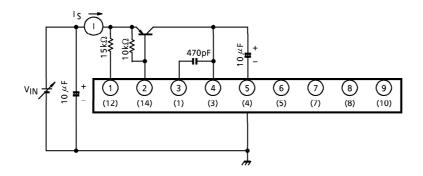

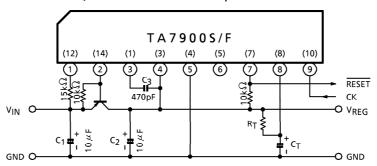

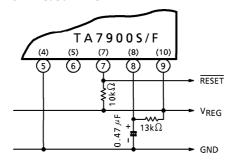

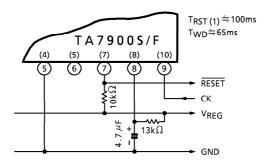

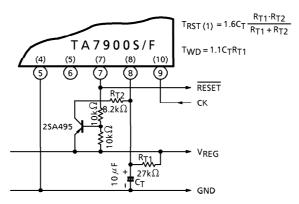

TEST CIRCUIT (Circles O indicate the pin numbers on the TA7900S or TA7900F.)

# 1. V<sub>REG</sub>

# 2. VOL (RESET)

# 3. ILEAK (RESET)

# 4. IN (TC)

5.  $V_{IH}$ ,  $V_{IL}$  (TC),  $V_{IH}$ ,  $V_{IL}$  (CK)

# 6. I<sub>IN</sub> (CK)

# 7. VRESET \ TWD \ TRST (1) \ TRST (2)

# 8. Is

### **TYPICAL CHARACTERISTICS**

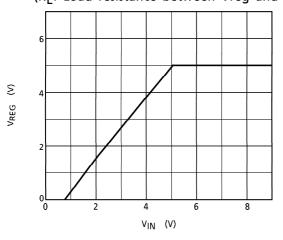

1. Input-output characteristic ( $R_L = 25\Omega$ , external transistor 2SA968-Y) ( $R_L$ : Load resistance between Vreg and GND)

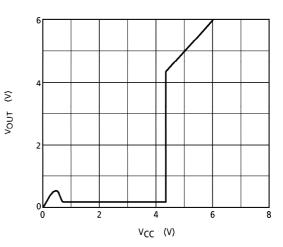

2. Reset Output Characteristic

3. Output Adjusting Resistance Characteristic

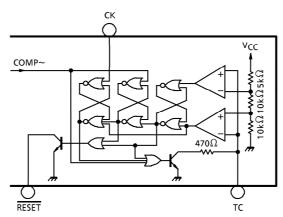

### RESET TIMER EQUIVALENT CIRCUIT

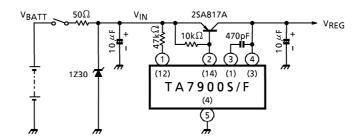

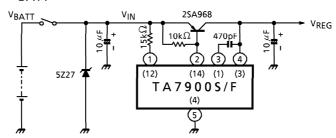

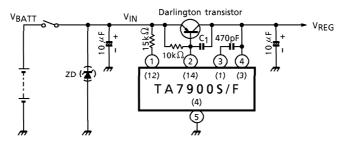

**EXAMPLE OF APPLICATION CIRCUIT** (Circles O indicate the pin numbers on the TA7900S or TA7900F.)

- \* Cautions for Wiring

- 1. C<sub>1</sub> and C<sub>2</sub> are for absorbing disturbance, noise, etc. Connect them as close to the IC as possible.

- 2. C<sub>3</sub> is for phase compensation. Also, connect C<sub>3</sub> close to the IC.

### 120 Vpeak (200ms) LOAD DUMP

Low Output Current Circuit

I<sub>LOAD</sub> = 10mA Max., V<sub>BATT</sub> = 6 to 17V

2. High Output Current Circuit  $I_{LOAD} = 300 \text{mA}$  Max.,  $V_{BATT} = 6 \sim 17 \text{V}$

#### **EXAMPLE OF APPLICATION CIRCUIT USING DARLINGTON TRANSISTOR**

\* Select a C<sub>1</sub> value according to the working condition -- typically above 2000pF. Insert ZD when necessary.

### APPLICATION CIRCUIT OF WATCHDOG/RESET TIMER

1. T<sub>RST (1)</sub> ≒10ms······Power-On Reset Timer

2. T<sub>RST (1)</sub> ≒1.5T<sub>WD</sub>

3. T<sub>RST (1)</sub> ≒100ms, T<sub>WD</sub>≒300ms

### 4. Recommended Conditions

| PART NAME                                 | MIN. | MAX. | UNIT    |

|-------------------------------------------|------|------|---------|

| C <sub>T</sub>                            | 0.01 | 100  | $\mu$ F |

| R <sub>T</sub>                            | 5    | 100  | kΩ      |

| R <sub>T1</sub>                           | _    | 100  | kΩ      |

| R <sub>T1</sub> // R <sub>T2</sub> (Note) | 5    | _    | kΩ      |

(Note)  $R_{T1} // R_{T2} = (R_{T1} \times R_{T2}) / (R_{T1} + R_{T2})$

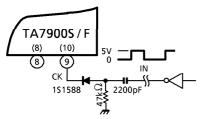

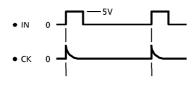

# **CK INPUT APPLICATION CIRCUIT**

Capacitor Coupling

Timing Chart

The capacitor coupling allows reset pulses to be supplied intermittently from the  $\overline{\text{RESET}}$  pin whether the input level (IN) is high or low.

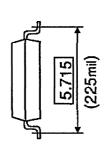

### OUTLINE DRAWING SIP9-P-2.54A

Unit: mm

Weight: 0.92g (Typ.)

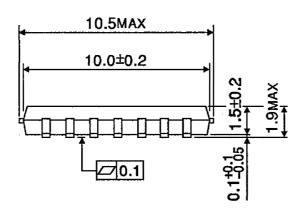

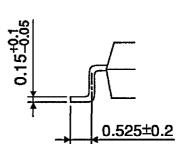

# **OUTLINE DRAWING**

SOP14-P-225-1.27

Unit: mm

Weight: 0.2g (Typ.)